-

; ) 石英晶片(频率片)对晶振频率的影响

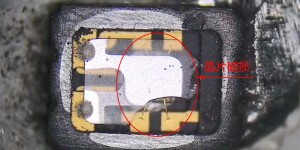

2024-09-03(晶振内置石英晶片脏污且破损图片) 关于石英晶片(频率片)对晶振频率的影响,晶诺威科技介绍如下: 晶片无损加工工艺基本流程 1、移载定位 2、工装定位清洗 3、镀银 晶诺威科技晶片生产流程及优势 1、提高晶片研磨技术,实时监控晶片厚度,确保晶片表面平滑,有效增强频率主波信号输出稳定,使副波(谐波)信…

石英晶片(频率片)对晶振频率的影响

2024-09-03(晶振内置石英晶片脏污且破损图片) 关于石英晶片(频率片)对晶振频率的影响,晶诺威科技介绍如下: 晶片无损加工工艺基本流程 1、移载定位 2、工装定位清洗 3、镀银 晶诺威科技晶片生产流程及优势 1、提高晶片研磨技术,实时监控晶片厚度,确保晶片表面平滑,有效增强频率主波信号输出稳定,使副波(谐波)信… -

; ) 关于芯片外部晶振放置位置的说明

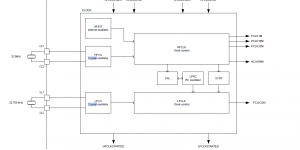

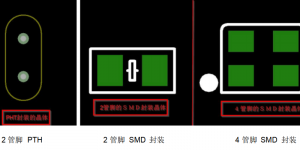

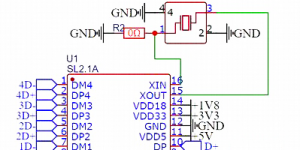

2024-08-22SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os…

关于芯片外部晶振放置位置的说明

2024-08-22SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os… -

; ) 电子设计中的EMI和EMC有什么区别?

2024-06-10(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…

电子设计中的EMI和EMC有什么区别?

2024-06-10(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele… -

; ) 晶振会产生电磁波干扰吗?

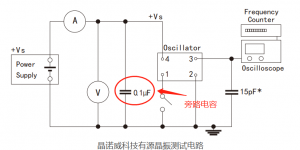

2024-05-12晶振会产生电磁波干扰吗? 答:会的。 晶诺威科技解释如下: 传统排除晶振电磁波干扰的方式:在回路中加入磁珠、滤波器、接地回路、以及金属屏蔽罩。作为晶振厂家,晶诺威科技也在优化晶振本身材质及电路设计,尽最大可能降低晶振对外界的干扰,同时,也增强了自身抗(来自外界的)干扰能力。 在有源晶振方面,则增加了…

晶振会产生电磁波干扰吗?

2024-05-12晶振会产生电磁波干扰吗? 答:会的。 晶诺威科技解释如下: 传统排除晶振电磁波干扰的方式:在回路中加入磁珠、滤波器、接地回路、以及金属屏蔽罩。作为晶振厂家,晶诺威科技也在优化晶振本身材质及电路设计,尽最大可能降低晶振对外界的干扰,同时,也增强了自身抗(来自外界的)干扰能力。 在有源晶振方面,则增加了… -

; ) 关于展频晶振抗干扰与时钟精度的冲突问题

2024-01-19关于展频晶振抗干扰与时钟精度的冲突问题,晶诺威科技分析如下: Every electronic product designer has to deal with the issue of electromagnetic compatibility (EMC) or electromagnetic …

关于展频晶振抗干扰与时钟精度的冲突问题

2024-01-19关于展频晶振抗干扰与时钟精度的冲突问题,晶诺威科技分析如下: Every electronic product designer has to deal with the issue of electromagnetic compatibility (EMC) or electromagnetic … -

; ) 晶振布线为何要加粗?

2023-08-24晶振布线为何要加粗? 答:减少晶振信号来自电路的干扰,因为电路过细,电阻会增大,电流会趋于不稳定,容易造成杂讯。 解释: 晶振线路加粗和尽量缩短与芯片之间距离是一个目的,就是减少信号电路中的阻抗及干扰,保障晶振频率信号传输后的精准性及稳定性。 电磁干扰对晶振性能的影响原因 1、电磁场中的电流感应:…

晶振布线为何要加粗?

2023-08-24晶振布线为何要加粗? 答:减少晶振信号来自电路的干扰,因为电路过细,电阻会增大,电流会趋于不稳定,容易造成杂讯。 解释: 晶振线路加粗和尽量缩短与芯片之间距离是一个目的,就是减少信号电路中的阻抗及干扰,保障晶振频率信号传输后的精准性及稳定性。 电磁干扰对晶振性能的影响原因 1、电磁场中的电流感应:… -

; ) 关于晶体振荡器电路布线引发的问题(Layout Issues)

2023-06-06关于晶体振荡器电路布线引发的问题(Layout Issues),晶诺威科技解释如下: Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is cri…

关于晶体振荡器电路布线引发的问题(Layout Issues)

2023-06-06关于晶体振荡器电路布线引发的问题(Layout Issues),晶诺威科技解释如下: Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is cri… -

; ) 关于晶体振荡器电路Noise Immunity(抗噪声能力)解决方案

2023-05-31关于晶体振荡器电路Noise Immunity(抗噪声能力)解决方案,晶诺威科技说明如下: Noise is a common cause of oscillator failures; therefore, it’s important to know how to make the oscill…

关于晶体振荡器电路Noise Immunity(抗噪声能力)解决方案

2023-05-31关于晶体振荡器电路Noise Immunity(抗噪声能力)解决方案,晶诺威科技说明如下: Noise is a common cause of oscillator failures; therefore, it’s important to know how to make the oscill… -

; ) 晶振时钟信号干扰源:是寄生电容、杂散电容还是分布电容?

2022-07-18寄生的含义就是本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容,又称杂散电容。 寄生电容本身不是电容,根据电容的原理我们可以知道,电容是由两个极板和绝缘介质构成的,那么寄生电容是无法避免的。比如一个电路有很多电线,电线与电线之间形成的电容叫做寄生…

晶振时钟信号干扰源:是寄生电容、杂散电容还是分布电容?

2022-07-18寄生的含义就是本来没有在那个地方设计电容,但由于布线之间总是有互容,互容就好像是寄生在布线之间的一样,所以叫寄生电容,又称杂散电容。 寄生电容本身不是电容,根据电容的原理我们可以知道,电容是由两个极板和绝缘介质构成的,那么寄生电容是无法避免的。比如一个电路有很多电线,电线与电线之间形成的电容叫做寄生…

; )