-

; ) 关于时钟信号分频,倍频和锁相环PLL电路

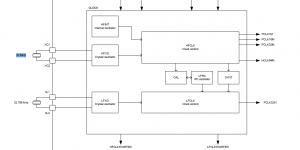

2022-07-06关于时钟信号分频,倍频和锁相环PLL电路相关知识,晶诺威科技整理如下: 锁相环振荡器(PLL): 锁相环是一种反馈控制系统,它可以将输入信号的相位锁定到晶振产生的输出信号上。每种振荡器的设计和应用都有其特定的要求,选择合适的驱动方式取决于所需的频率稳定性、功耗、尺寸、成本和应用场合。在设计和应用时,…

关于时钟信号分频,倍频和锁相环PLL电路

2022-07-06关于时钟信号分频,倍频和锁相环PLL电路相关知识,晶诺威科技整理如下: 锁相环振荡器(PLL): 锁相环是一种反馈控制系统,它可以将输入信号的相位锁定到晶振产生的输出信号上。每种振荡器的设计和应用都有其特定的要求,选择合适的驱动方式取决于所需的频率稳定性、功耗、尺寸、成本和应用场合。在设计和应用时,… -

; ) 晶振频率分频/倍频/预分频/后分频原理

2021-11-18晶振频率频分/倍频/预分频/后分频 分频 一个晶振只有一个 固有频率,通过分频、倍频可以扩展出许多频率,这样就不必每个频率配一个晶振了。晶振的原信号通过N分频,频率变为原来的1/N,周期变为原来的N倍。(时域上)也就是说,经过原来N个周期,现在信号才跳变一次。 倍频 N倍频-->…

晶振频率分频/倍频/预分频/后分频原理

2021-11-18晶振频率频分/倍频/预分频/后分频 分频 一个晶振只有一个 固有频率,通过分频、倍频可以扩展出许多频率,这样就不必每个频率配一个晶振了。晶振的原信号通过N分频,频率变为原来的1/N,周期变为原来的N倍。(时域上)也就是说,经过原来N个周期,现在信号才跳变一次。 倍频 N倍频-->… -

; ) 晶振锁相环电路原理介绍

2020-07-18近年来,基于即时视频传输越来越受到广泛需求,网络通信的大量数据的非延时性传输与交换问题也随之展现在我们眼前。 在这种情况下,高速通信基站对高频且输出信号稳定的基准信号源的需求已经迫在眉睫。通常,从MHz频带的AT型晶振获得高频振荡时需要将石英片加工得很薄,因为AT型石英晶体的频率因其厚…

晶振锁相环电路原理介绍

2020-07-18近年来,基于即时视频传输越来越受到广泛需求,网络通信的大量数据的非延时性传输与交换问题也随之展现在我们眼前。 在这种情况下,高速通信基站对高频且输出信号稳定的基准信号源的需求已经迫在眉睫。通常,从MHz频带的AT型晶振获得高频振荡时需要将石英片加工得很薄,因为AT型石英晶体的频率因其厚…