-

; ) 晶振的负载电容不等于其匹配电容

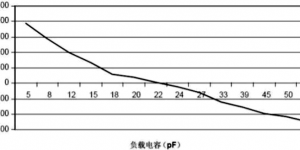

2022-07-31负载电容CL是电路中跨接无源晶振两端的总的有效电容,它并不是指无源晶振外接的匹配电容。负载电容CL主要影响负载谐振频率和等效负载谐振电阻,与无源晶振⼀起决定振荡器电路的⼯作频率。通过调整负载电容的大小,就可以将振荡器的⼯作频率微调到靠近标称值。 负载电容CL是⽆源晶振⾮常重要的参数,因为⽆源晶振属于…

晶振的负载电容不等于其匹配电容

2022-07-31负载电容CL是电路中跨接无源晶振两端的总的有效电容,它并不是指无源晶振外接的匹配电容。负载电容CL主要影响负载谐振频率和等效负载谐振电阻,与无源晶振⼀起决定振荡器电路的⼯作频率。通过调整负载电容的大小,就可以将振荡器的⼯作频率微调到靠近标称值。 负载电容CL是⽆源晶振⾮常重要的参数,因为⽆源晶振属于… -

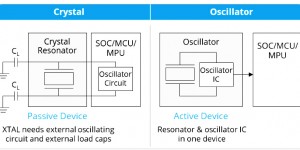

; ) 有源晶振和无源晶振电路差异及应用注意事项

2022-05-19关于有源晶振和无源晶振电路差异,晶诺威科技解释如下: 有源晶振不需要匹配电容起振便可直接工作,从逻辑上讲,直接上电即可起振; 无源晶振需要在起振电路中匹配合适的电容(启动电容)才能正常起振。在起振电路中,在没有外接匹配电容的情况下,无源晶振也可以起振,但容易发生频偏超差问题,主要体现为“偏正”。 晶…

有源晶振和无源晶振电路差异及应用注意事项

2022-05-19关于有源晶振和无源晶振电路差异,晶诺威科技解释如下: 有源晶振不需要匹配电容起振便可直接工作,从逻辑上讲,直接上电即可起振; 无源晶振需要在起振电路中匹配合适的电容(启动电容)才能正常起振。在起振电路中,在没有外接匹配电容的情况下,无源晶振也可以起振,但容易发生频偏超差问题,主要体现为“偏正”。 晶… -

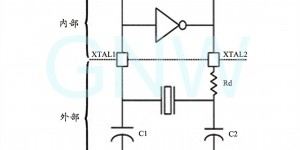

; ) 无源晶振振荡条件与接地电容之间的关系

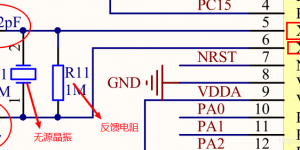

2022-05-16关于无源晶振振荡条件与接地电容之间的关系,晶诺威科技介绍如下: 各种逻辑芯片的无源晶振引脚可以等效为电容三点式振荡器。 无源晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。在无源晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十M 欧之…

无源晶振振荡条件与接地电容之间的关系

2022-05-16关于无源晶振振荡条件与接地电容之间的关系,晶诺威科技介绍如下: 各种逻辑芯片的无源晶振引脚可以等效为电容三点式振荡器。 无源晶振引脚的内部通常是一个反相器, 或者是奇数个反相器串联。在无源晶振输出引脚 XO 和晶振输入引脚 XI 之间用一个电阻连接, 对于 CMOS 芯片通常是数 M 到数十M 欧之… -

; ) 8MHz无源晶振典型电路:8MHz晶振需要匹配多大电容?

2022-05-11(贴片式无源晶振SMD3225-4pad) 晶诺威科技生产的贴片无源晶振8M常见负载电容CL为12PF和20PF,建议如下: 当晶振负载电容CL=12PF时,建议匹配电容在15-18PF之间。 当晶振负载电容CL=20PF时,建议匹配电容在27-33PF之间。 由以上可见,8MHz晶振…

8MHz无源晶振典型电路:8MHz晶振需要匹配多大电容?

2022-05-11(贴片式无源晶振SMD3225-4pad) 晶诺威科技生产的贴片无源晶振8M常见负载电容CL为12PF和20PF,建议如下: 当晶振负载电容CL=12PF时,建议匹配电容在15-18PF之间。 当晶振负载电容CL=20PF时,建议匹配电容在27-33PF之间。 由以上可见,8MHz晶振… -

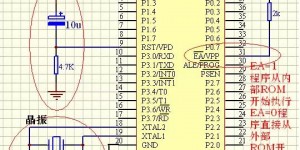

; ) 数字电路的时钟信号源:无源晶振电路与有源晶振电路对比

2022-01-10关于数字电路的时钟信号源:无源晶振电路与有源晶振电路对比如下: 对于数字电路中基于时钟信号才能工作的芯片来说,有两种选择: 芯片内置时钟电路,通过编程器配置或外部设置就能产生时钟信号,内部时钟往往频率精度较低。 外接晶振电路产生时钟信号。由晶振提供的时钟信号具备高精度及高稳定性等特点。 外部晶振…

数字电路的时钟信号源:无源晶振电路与有源晶振电路对比

2022-01-10关于数字电路的时钟信号源:无源晶振电路与有源晶振电路对比如下: 对于数字电路中基于时钟信号才能工作的芯片来说,有两种选择: 芯片内置时钟电路,通过编程器配置或外部设置就能产生时钟信号,内部时钟往往频率精度较低。 外接晶振电路产生时钟信号。由晶振提供的时钟信号具备高精度及高稳定性等特点。 外部晶振… -

; ) 32.768KHz晶振负载电容CL选错导致晶振不起振案例分析

2021-11-25(SMART LOCK:智能锁) 客户反馈在批量生产阶段,32.768KHz晶振不起振,导致所生产的智能锁开机系统紊乱,无法正常使用。 通过与客户沟通,了解到:该类型智能锁开机后,芯片捕捉32.768KHz晶振提供的时钟信号,完成系统诊断无误后,方可正常开机。问题就发生在芯片捕捉时钟信号失败这个环节…

32.768KHz晶振负载电容CL选错导致晶振不起振案例分析

2021-11-25(SMART LOCK:智能锁) 客户反馈在批量生产阶段,32.768KHz晶振不起振,导致所生产的智能锁开机系统紊乱,无法正常使用。 通过与客户沟通,了解到:该类型智能锁开机后,芯片捕捉32.768KHz晶振提供的时钟信号,完成系统诊断无误后,方可正常开机。问题就发生在芯片捕捉时钟信号失败这个环节… -

; ) 晶振的频率误差,负载电容,匹配电容及IC内置补偿电容

2021-11-20晶振能够产生中央处理器(CPU)执行指令所必须要的时钟频率信号,CPU一切指令的执行都是建立在这个基础上的,时钟信号频率越高,通常CPU的运行速度也就越快。需要注意的几个晶振重要参数如下: 标称频率 在1~200MHz之间,比如32.768Hz、8MHz、12MHz、24MHz、125MHz等,更高…

晶振的频率误差,负载电容,匹配电容及IC内置补偿电容

2021-11-20晶振能够产生中央处理器(CPU)执行指令所必须要的时钟频率信号,CPU一切指令的执行都是建立在这个基础上的,时钟信号频率越高,通常CPU的运行速度也就越快。需要注意的几个晶振重要参数如下: 标称频率 在1~200MHz之间,比如32.768Hz、8MHz、12MHz、24MHz、125MHz等,更高… -

; ) 无源晶振频偏案例及调校措施

2021-11-16(显示器显像故障) 设备不良现象表现为显示器不出彩或彩条等问题。在排除ISP(Image Signal Processing 图像信号处理系统)自身寄存器设定与TV Decoder输出周边參数不对的因素外,电路应用中的问题很有可能为晶振频偏所致。 举例:某款安防视频监控采用的晶振规格参数如下: 晶振…

无源晶振频偏案例及调校措施

2021-11-16(显示器显像故障) 设备不良现象表现为显示器不出彩或彩条等问题。在排除ISP(Image Signal Processing 图像信号处理系统)自身寄存器设定与TV Decoder输出周边參数不对的因素外,电路应用中的问题很有可能为晶振频偏所致。 举例:某款安防视频监控采用的晶振规格参数如下: 晶振… -

; ) 晶振的负载电容,匹配电容,静电容及杂散电容分别指什么?

2021-09-14有关晶振电容相关资料,晶诺威科技汇总如下: CL CL(负载电容load capacitance)是一个非常至关重要的参数。如果晶振的负载电容与晶振外部两端连接的电容参数匹配不正确的话,很容易造成频率偏差,精度误差等,从而导致晶振无法达到最终的精准要求。当然也存在对负载电容参数不是特别严格的厂家。R…

晶振的负载电容,匹配电容,静电容及杂散电容分别指什么?

2021-09-14有关晶振电容相关资料,晶诺威科技汇总如下: CL CL(负载电容load capacitance)是一个非常至关重要的参数。如果晶振的负载电容与晶振外部两端连接的电容参数匹配不正确的话,很容易造成频率偏差,精度误差等,从而导致晶振无法达到最终的精准要求。当然也存在对负载电容参数不是特别严格的厂家。R…

; )