-

; ) 差分晶振:差分信号与差分传输

2022-12-12差分信号(Differential signal) 指两信号振幅相等,但相位相反的信号。 差分传输 差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相同,相位相反。在这两根线上的传输的信号就是差分信号。信号接收端比较这两个电压的差值…

差分晶振:差分信号与差分传输

2022-12-12差分信号(Differential signal) 指两信号振幅相等,但相位相反的信号。 差分传输 差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相同,相位相反。在这两根线上的传输的信号就是差分信号。信号接收端比较这两个电压的差值… -

; ) LVDS/LVPECL/HCSL输出差分晶振SMD5032规格参数

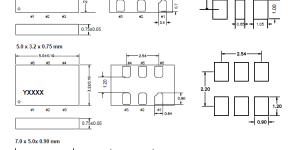

2022-11-30(Bottom View) LVDS/LVPECL/HCSL输出差分晶振SMD5032规格参数 1、SMD5032差分晶振LVDS输出 特点及优势 贴片金属封装LVDS差分高频晶振 LVDS信号输出,高频率输出范围: 10MHz~1500MHz 2.5V/3.3V低工作电压,低功耗,高精度 支持三态…

LVDS/LVPECL/HCSL输出差分晶振SMD5032规格参数

2022-11-30(Bottom View) LVDS/LVPECL/HCSL输出差分晶振SMD5032规格参数 1、SMD5032差分晶振LVDS输出 特点及优势 贴片金属封装LVDS差分高频晶振 LVDS信号输出,高频率输出范围: 10MHz~1500MHz 2.5V/3.3V低工作电压,低功耗,高精度 支持三态… -

; ) LVDS/LVPECL/HCSL输出差分晶振SMD7050电气参数说明

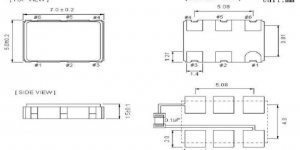

2022-11-24(差分晶振脚位功能说明) LVDS/LVPECL/HCSL输出差分晶振SMD7050电气参数说明如下: 1、SMD7050差分晶振LVDS输出 特点及优势 贴片金属封装LVDS差分高频晶振 LVDS信号输出,高频率输出范围: 10MHz~1500MHz 振荡模式:基频/三倍频/PLL 2.5V/3.…

LVDS/LVPECL/HCSL输出差分晶振SMD7050电气参数说明

2022-11-24(差分晶振脚位功能说明) LVDS/LVPECL/HCSL输出差分晶振SMD7050电气参数说明如下: 1、SMD7050差分晶振LVDS输出 特点及优势 贴片金属封装LVDS差分高频晶振 LVDS信号输出,高频率输出范围: 10MHz~1500MHz 振荡模式:基频/三倍频/PLL 2.5V/3.… -

; ) LVDS/LVPECL/HCSL Output差分晶振SMD3225规格参数介绍

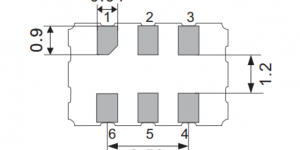

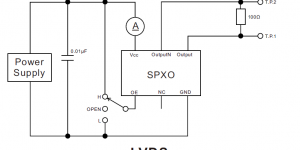

2022-11-22LVDS/LVPECL/HCSL Output差分晶振SMD3225规格参数介绍如下: LVDS Output 差分晶振SMD3225 测试电路 小尺寸贴片金属封装LVDS晶体振荡器 LVDS信号输出,高频率输出范围: 10MHz~250MHz 2.5V/3.3V低工作电…

LVDS/LVPECL/HCSL Output差分晶振SMD3225规格参数介绍

2022-11-22LVDS/LVPECL/HCSL Output差分晶振SMD3225规格参数介绍如下: LVDS Output 差分晶振SMD3225 测试电路 小尺寸贴片金属封装LVDS晶体振荡器 LVDS信号输出,高频率输出范围: 10MHz~250MHz 2.5V/3.3V低工作电… -

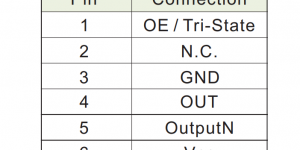

; ) 关于差分晶振5号脚Complementary clock output的说明

2022-11-22PIN#1:Tri-State PIN#2:N.C PIN#3:GND PIN#4:Output PIN#5:Comp. Output PIN#6:VDD 关于差分晶振5号脚Complementary clock output的说明如下: Complementary clock out…

关于差分晶振5号脚Complementary clock output的说明

2022-11-22PIN#1:Tri-State PIN#2:N.C PIN#3:GND PIN#4:Output PIN#5:Comp. Output PIN#6:VDD 关于差分晶振5号脚Complementary clock output的说明如下: Complementary clock out… -

; ) 差分信号线中间可否加地线?

2022-07-10差分信号中间一般是不能加地线。因为差分信号的应用原理最重要的一点便是利用差分信号间相互耦合(coupling)所带来的好处,如flux cancellation,抗噪声(noise immunity)能力等。若在中间加地线,便会破坏耦合效应。 附:MEMS差分振荡器SiT9121主要参数: 频率范围…

差分信号线中间可否加地线?

2022-07-10差分信号中间一般是不能加地线。因为差分信号的应用原理最重要的一点便是利用差分信号间相互耦合(coupling)所带来的好处,如flux cancellation,抗噪声(noise immunity)能力等。若在中间加地线,便会破坏耦合效应。 附:MEMS差分振荡器SiT9121主要参数: 频率范围… -

; ) 晶振输出波形:CMOS,LVPECL和LVDS

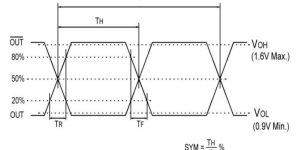

2022-05-12在数字电路中,我们需要选择晶振输出波形以匹配振荡器将在系统中驱动的负载。最常见的输出之一是CMOS,即以驱动逻辑电平输入。CMOS输出将是在地电位和系统的Vdd轨之间摆动的方波。对于高于约100MHz的较高频率,通常使用差分方波。 具备差分方波输出的振荡器具有两个180°异相的输出、具有快速上升和下…

晶振输出波形:CMOS,LVPECL和LVDS

2022-05-12在数字电路中,我们需要选择晶振输出波形以匹配振荡器将在系统中驱动的负载。最常见的输出之一是CMOS,即以驱动逻辑电平输入。CMOS输出将是在地电位和系统的Vdd轨之间摆动的方波。对于高于约100MHz的较高频率,通常使用差分方波。 具备差分方波输出的振荡器具有两个180°异相的输出、具有快速上升和下… -

; ) SMD3225 TXC差分晶振156.25MHz LVPECL规格书及使用说明

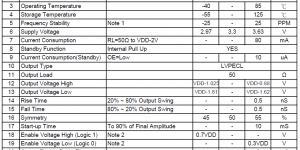

2021-08-19SMD3225 TXC差分晶振156.25MHz电气参数介绍如下: FACTORY(生产工厂):TXC OUTPUT WAVEFORM(输出波形):LVPECL TXC P/N(TXC料号): DBA5600011 PRODUCT TYPE(产品类型): SMD LVPECL CXO 3.2mm*2…

SMD3225 TXC差分晶振156.25MHz LVPECL规格书及使用说明

2021-08-19SMD3225 TXC差分晶振156.25MHz电气参数介绍如下: FACTORY(生产工厂):TXC OUTPUT WAVEFORM(输出波形):LVPECL TXC P/N(TXC料号): DBA5600011 PRODUCT TYPE(产品类型): SMD LVPECL CXO 3.2mm*2… -

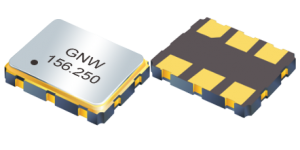

; ) 156.25MHz小型低抖动差分晶振介绍

2021-02-23(晶诺威科差分晶振产品图) 晶诺威科技研发生产的156.25MHz差分晶振介绍如下: 当今,DCI(Downlink Control Information)互联,5G数据高速传输等相关设备正在日新月异的迅猛发展。这些设备实现稳定高速大数据传输离不开pam4(4 Pulse Amplitude Mo…

156.25MHz小型低抖动差分晶振介绍

2021-02-23(晶诺威科差分晶振产品图) 晶诺威科技研发生产的156.25MHz差分晶振介绍如下: 当今,DCI(Downlink Control Information)互联,5G数据高速传输等相关设备正在日新月异的迅猛发展。这些设备实现稳定高速大数据传输离不开pam4(4 Pulse Amplitude Mo… -

; ) 关于差分晶振的时钟逻辑类型介绍

2021-02-22常见差分晶振的差分逻辑信号类型及特点介绍如下: 每个可用的时钟逻辑类型(LVPECL、HCSL、CML和LVDS)使用的共模电压和摆幅电平低于下一个时钟逻辑类型,在任何给定的系统设计中,必须设计驱动器侧和接收器侧之间的时钟逻辑转换。通过在它们之间增加衰减电阻和偏置电路来将一个差分时钟转换为其他类型的…

关于差分晶振的时钟逻辑类型介绍

2021-02-22常见差分晶振的差分逻辑信号类型及特点介绍如下: 每个可用的时钟逻辑类型(LVPECL、HCSL、CML和LVDS)使用的共模电压和摆幅电平低于下一个时钟逻辑类型,在任何给定的系统设计中,必须设计驱动器侧和接收器侧之间的时钟逻辑转换。通过在它们之间增加衰减电阻和偏置电路来将一个差分时钟转换为其他类型的…