-

; ) 晶诺威科技产无源贴片晶振EMI消除方案

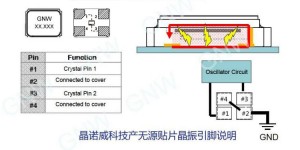

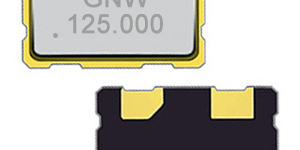

2022-04-27Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen…

晶诺威科技产无源贴片晶振EMI消除方案

2022-04-27Terminals 2 and 4 on a Genuway crystal unit are connected electrically to the metal cover of the crystal. 晶诺威科技产无源贴片晶振焊盘#2和#4与金属外壳连接。 Genuway recommen… -

; ) 降低晶振振荡电路中EMI的解决方案是什么?

2022-04-11Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric…

降低晶振振荡电路中EMI的解决方案是什么?

2022-04-11Electromagnetic interference (or EMI, also called radio frequency interference or RFI) is a (usually undesirable) disturbance that affects an electric… -

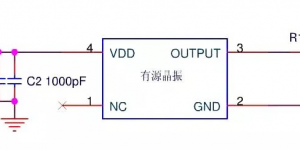

; ) 有源晶振的使用说明及注意事项

2021-11-29有源晶振的使用说明及注意事项 1、有源晶振内置含IC在内的集成电路,请注意防静电保护。 2、若VCC-GND之间有旁路电容,为了防止施加过大电压和防止过电流,请将旁路电容(0.01uF)放置在尽可能靠近(+DC-GND)端。容量是参考值,频率特性因电容类型而异,请使用适当的频率特性的电容器。 3、施…

有源晶振的使用说明及注意事项

2021-11-29有源晶振的使用说明及注意事项 1、有源晶振内置含IC在内的集成电路,请注意防静电保护。 2、若VCC-GND之间有旁路电容,为了防止施加过大电压和防止过电流,请将旁路电容(0.01uF)放置在尽可能靠近(+DC-GND)端。容量是参考值,频率特性因电容类型而异,请使用适当的频率特性的电容器。 3、施… -

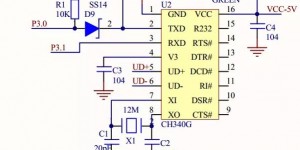

; ) 晶振类型,晶振参数,晶振应用及晶振电路抗干扰设计

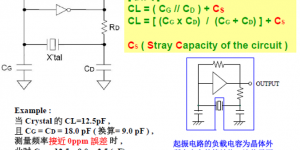

2021-09-15(RTC晶振32.768KHz外接电容与负载电容匹配计算方法) 晶振的作用是为数字电路提供一个稳定的工作时钟信号。没有晶振,数字电路无法工作。 晶振类型 我们常说的晶振,包含两种。一种需要加驱动电路才能产生频率信号,这类晶振叫晶振谐振器,又被称之为无源晶振,比如常见的49S晶振、49SMD晶振、圆柱…

晶振类型,晶振参数,晶振应用及晶振电路抗干扰设计

2021-09-15(RTC晶振32.768KHz外接电容与负载电容匹配计算方法) 晶振的作用是为数字电路提供一个稳定的工作时钟信号。没有晶振,数字电路无法工作。 晶振类型 我们常说的晶振,包含两种。一种需要加驱动电路才能产生频率信号,这类晶振叫晶振谐振器,又被称之为无源晶振,比如常见的49S晶振、49SMD晶振、圆柱… -

; ) 关于晶振偶次谐波干扰问题的三点建议

2021-07-16(晶诺威科技贴片晶振产品) 首先说明,以下内容主要针对后期产品进行整改的办法。如果在PCB布线设计初期,可以从电路板的结构设计上进行更改,这样更有效。 基于PCB设计及布线可能存在的复杂性及/或不合理性,我们有时会遇到晶振谐波干扰的问题,建议从以下三个方面考虑: 1、如果针对被干扰的设备采取防电磁干…

关于晶振偶次谐波干扰问题的三点建议

2021-07-16(晶诺威科技贴片晶振产品) 首先说明,以下内容主要针对后期产品进行整改的办法。如果在PCB布线设计初期,可以从电路板的结构设计上进行更改,这样更有效。 基于PCB设计及布线可能存在的复杂性及/或不合理性,我们有时会遇到晶振谐波干扰的问题,建议从以下三个方面考虑: 1、如果针对被干扰的设备采取防电磁干… -

; ) 如何解决有源晶振对电源的干扰问题?

2020-12-24在有源晶振的电路应用中,我们该如何尽量避免其对电源的干扰呢? 晶诺威科技建议PCB设计如下: 1、晶振外壳接地设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。 2、晶振所在层铺地设计,目的是防止晶振信号干扰其它层。 3、建议晶振下面不要布线,其周围5毫米范围内不要设计布线及安置其它电子元件…

如何解决有源晶振对电源的干扰问题?

2020-12-24在有源晶振的电路应用中,我们该如何尽量避免其对电源的干扰呢? 晶诺威科技建议PCB设计如下: 1、晶振外壳接地设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。 2、晶振所在层铺地设计,目的是防止晶振信号干扰其它层。 3、建议晶振下面不要布线,其周围5毫米范围内不要设计布线及安置其它电子元件… -

; ) 晶振PCB正确布线需要哪些注意事项?

2020-10-09晶振PCB正确布线的重要性 晶振PCB正确布线直接决定着电路板是否上电后正常及稳定工作,因此其重要性千万不可忽略。 如何避免晶振受干扰? 为了避免晶振受到PCB边缘的干扰,通常可以采取以下措施:将晶振放置在离PCB边缘一定距离的位置,以减少外界干扰的影响;在晶振周围设置合适的屏蔽罩,以减少外界电磁辐…

晶振PCB正确布线需要哪些注意事项?

2020-10-09晶振PCB正确布线的重要性 晶振PCB正确布线直接决定着电路板是否上电后正常及稳定工作,因此其重要性千万不可忽略。 如何避免晶振受干扰? 为了避免晶振受到PCB边缘的干扰,通常可以采取以下措施:将晶振放置在离PCB边缘一定距离的位置,以减少外界干扰的影响;在晶振周围设置合适的屏蔽罩,以减少外界电磁辐… -

; ) PCB晶振布线抗干扰(EMI)设计介绍

2020-10-06作为频率电子元器件,晶振设计是电子产品中电路元件和器件的支撑件,它提供电路元件和器件之间的电气连接。目前电子产品日趋小型化,PCB的密度也随之越来越高。PCB设计对抗干扰能性影响很大,因此在进行PCB设计时,首先,要考虑PCB尺寸大小。PCB尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增…

PCB晶振布线抗干扰(EMI)设计介绍

2020-10-06作为频率电子元器件,晶振设计是电子产品中电路元件和器件的支撑件,它提供电路元件和器件之间的电气连接。目前电子产品日趋小型化,PCB的密度也随之越来越高。PCB设计对抗干扰能性影响很大,因此在进行PCB设计时,首先,要考虑PCB尺寸大小。PCB尺寸过大时,印制线条长,阻抗增加,抗噪声能力下降,成本也增… -

; ) 如何降低电磁对晶振时钟信号的干扰

2020-09-15电磁三要素是电磁干扰源、被干扰对象和传播电磁干扰的途径。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见而又非常重要的辐射源。尽管时钟信号与其他数据信号、控制信号的逻辑电平一般都是一样的,翻转速率一般也没有太大的差别(大多数总线数据率与时钟信号翻转速率之比是1:1或者1:2),但由于时钟…

如何降低电磁对晶振时钟信号的干扰

2020-09-15电磁三要素是电磁干扰源、被干扰对象和传播电磁干扰的途径。PCB板上安装的时钟信号是一种引起PCB板电磁兼容问题的常见而又非常重要的辐射源。尽管时钟信号与其他数据信号、控制信号的逻辑电平一般都是一样的,翻转速率一般也没有太大的差别(大多数总线数据率与时钟信号翻转速率之比是1:1或者1:2),但由于时钟… -

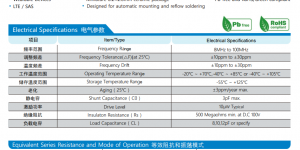

; ) 晶振选型需要注意哪些事项?

2020-07-19晶振根据频点、频差、负载、有源无源、封装、尺寸等多项参数的差异,可以分为成千上万种,的确令人眼花缭乱。那么,在晶振选型方面,我们首先需要注意什么呢?首先是晶振电气参数的选择,晶诺威科技归纳如下八点,仅供参考: 第一点:晶振的频率(Frequency) 如果PCBA上的芯片设计方案已经确定,则必须选择…

晶振选型需要注意哪些事项?

2020-07-19晶振根据频点、频差、负载、有源无源、封装、尺寸等多项参数的差异,可以分为成千上万种,的确令人眼花缭乱。那么,在晶振选型方面,我们首先需要注意什么呢?首先是晶振电气参数的选择,晶诺威科技归纳如下八点,仅供参考: 第一点:晶振的频率(Frequency) 如果PCBA上的芯片设计方案已经确定,则必须选择…