-

; ) 为何在OSC有源晶振Vdd脚与GND脚之间增加一个旁路电容?

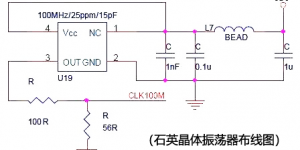

2022-07-29为何在有源晶振Vdd脚与GND脚之间增加一个旁路电容?晶诺威科技在有源晶振DATA BASE中,解释如下: To ensure optimal oscillator performance, place a by-pass capacitor of 0.1uF as close to the par…

为何在OSC有源晶振Vdd脚与GND脚之间增加一个旁路电容?

2022-07-29为何在有源晶振Vdd脚与GND脚之间增加一个旁路电容?晶诺威科技在有源晶振DATA BASE中,解释如下: To ensure optimal oscillator performance, place a by-pass capacitor of 0.1uF as close to the par… -

; ) 晶体谐振器/无源晶振振荡电路设计六个注意要点

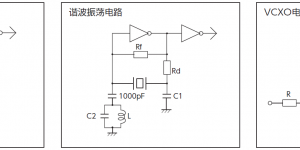

2022-05-05(晶体谐振器振荡电路设计图例) 晶体谐振器振荡电路设计六个注意要点归纳如下: 1、IC的选择 请务必选择与振荡频率相应的IC。 举例: 相当于4069UB : 从KHz带到8MHz附近 相当于7WU04 : 4~30MHz 相当于7WHU04 : 20~60MHz 2、反馈电阻Rf DC偏置用反馈电…

晶体谐振器/无源晶振振荡电路设计六个注意要点

2022-05-05(晶体谐振器振荡电路设计图例) 晶体谐振器振荡电路设计六个注意要点归纳如下: 1、IC的选择 请务必选择与振荡频率相应的IC。 举例: 相当于4069UB : 从KHz带到8MHz附近 相当于7WU04 : 4~30MHz 相当于7WHU04 : 20~60MHz 2、反馈电阻Rf DC偏置用反馈电… -

; ) 晶诺威科技产有源晶振EMI消除方案

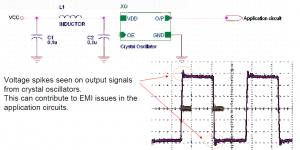

2022-04-27晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示:

晶诺威科技产有源晶振EMI消除方案

2022-04-27晶诺威科技产有源晶振EMI消除方案解释如下: 1、由下图可见有源晶振输出信号中出现电压尖峰,这可能会给应用电路带来EMI问题。如下图所示: 2、晶诺威科技建议在时钟信号输出端和 GND 之间添加旁路电容( 5-10 pF ),可以使输出波形平滑化,并可显著降低EMI。如下图所示: -

; ) 晶振激励功率和负性阻抗实测及计算方法

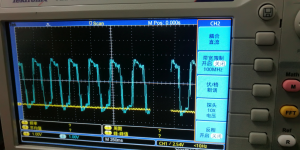

2020-11-10尽管在晶振振荡电路设计之前,我们都会从IC方案中获取晶振相关信息,如晶振封装、频率、频差、负载电容、工作电压等,但在晶振实际电路应用中,我们却会遇到一些具体问题,比如按照BOM采购晶振,在电路板上电后,发生晶振不良导致电路板显示不上电或某些功能失效等问题。在不少方案设计中,晶振的作用是…

晶振激励功率和负性阻抗实测及计算方法

2020-11-10尽管在晶振振荡电路设计之前,我们都会从IC方案中获取晶振相关信息,如晶振封装、频率、频差、负载电容、工作电压等,但在晶振实际电路应用中,我们却会遇到一些具体问题,比如按照BOM采购晶振,在电路板上电后,发生晶振不良导致电路板显示不上电或某些功能失效等问题。在不少方案设计中,晶振的作用是…