-

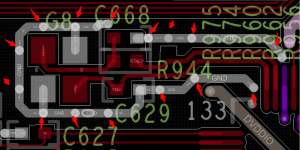

; ) 关于SMD3225晶振布线说明

2025-04-18关于SMD3225晶振布线设计,晶诺威科技说明如下: SMD3225晶振是一种表面贴装(SMD)封装的石英晶体振荡器,尺寸为3.2mm × 2.5mm。它在高频电路中广泛应用,如通信设备、消费电子和工业控制等。为了确保SMD3225晶振的正常工作和稳定性,PCB布线设计非常关键。以下是SMD3225…

关于SMD3225晶振布线说明

2025-04-18关于SMD3225晶振布线设计,晶诺威科技说明如下: SMD3225晶振是一种表面贴装(SMD)封装的石英晶体振荡器,尺寸为3.2mm × 2.5mm。它在高频电路中广泛应用,如通信设备、消费电子和工业控制等。为了确保SMD3225晶振的正常工作和稳定性,PCB布线设计非常关键。以下是SMD3225… -

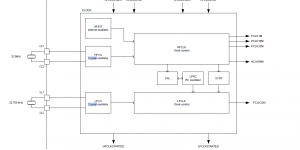

; ) 关于芯片外部晶振放置位置的说明

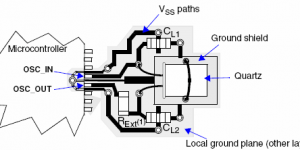

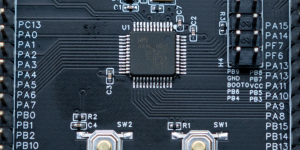

2024-08-22SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os…

关于芯片外部晶振放置位置的说明

2024-08-22SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os… -

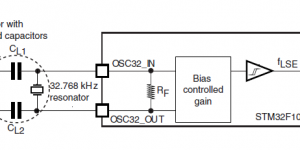

; ) 32.768KHz晶振走线需要等长吗?

2024-04-2632.768KHz晶振走线需要等长吗? 答:是的,32.768KHz晶振走线需要等长。 32.768KHz晶振尽量靠近芯片时钟信号端,时钟走线等长,等阻抗,以提高晶振输出频率的稳定度。如下图所示:

32.768KHz晶振走线需要等长吗?

2024-04-2632.768KHz晶振走线需要等长吗? 答:是的,32.768KHz晶振走线需要等长。 32.768KHz晶振尽量靠近芯片时钟信号端,时钟走线等长,等阻抗,以提高晶振输出频率的稳定度。如下图所示: -

; ) Crystal Oscillator PCB Layout Guidelines for Design

2024-04-25(Crystal Oscillator PCB Layout Guidelines for Design) When using a crystal oscillator in your PCB design, remember that it is very EMI sensitive and m…

Crystal Oscillator PCB Layout Guidelines for Design

2024-04-25(Crystal Oscillator PCB Layout Guidelines for Design) When using a crystal oscillator in your PCB design, remember that it is very EMI sensitive and m… -

; ) Layout issues of crystal oscillators

2024-04-23(Layout issues of crystal oscillators) Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is critica…

Layout issues of crystal oscillators

2024-04-23(Layout issues of crystal oscillators) Good layout practices are fundamental to the correct operation and reliability of the oscillator. It is critica… -

; ) 晶振走线需要等长吗?

2023-10-15晶振走线需要等长吗? 答:是的,需要等长且越短越好,尽量靠近芯片信号脚。 晶诺威科技解释如下: 晶振走线长度相等,高频信号受到的阻抗及干扰才会等同,不会产生差异。晶振走线的长度直接影响着信号受干扰的程度。由此可见,我们需要尽量降低类似干扰,保障晶振信号的纯净度,设备才会稳定运行。 电磁干扰对晶振性能…

晶振走线需要等长吗?

2023-10-15晶振走线需要等长吗? 答:是的,需要等长且越短越好,尽量靠近芯片信号脚。 晶诺威科技解释如下: 晶振走线长度相等,高频信号受到的阻抗及干扰才会等同,不会产生差异。晶振走线的长度直接影响着信号受干扰的程度。由此可见,我们需要尽量降低类似干扰,保障晶振信号的纯净度,设备才会稳定运行。 电磁干扰对晶振性能… -

; ) 晶振布线为何要加粗?

2023-08-24晶振布线为何要加粗? 答:减少晶振信号来自电路的干扰,因为电路过细,电阻会增大,电流会趋于不稳定,容易造成杂讯。 解释: 晶振线路加粗和尽量缩短与芯片之间距离是一个目的,就是减少信号电路中的阻抗及干扰,保障晶振频率信号传输后的精准性及稳定性。 电磁干扰对晶振性能的影响原因 1、电磁场中的电流感应:…

晶振布线为何要加粗?

2023-08-24晶振布线为何要加粗? 答:减少晶振信号来自电路的干扰,因为电路过细,电阻会增大,电流会趋于不稳定,容易造成杂讯。 解释: 晶振线路加粗和尽量缩短与芯片之间距离是一个目的,就是减少信号电路中的阻抗及干扰,保障晶振频率信号传输后的精准性及稳定性。 电磁干扰对晶振性能的影响原因 1、电磁场中的电流感应:… -

; ) 24MHz无源晶振EMC辐射超标问题分析与建议

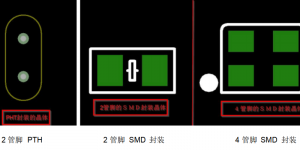

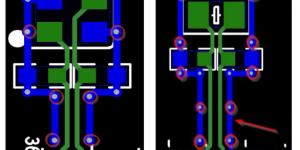

2023-06-15(4引线无源晶振与2引线无源晶振包地图示) 晶诺威科技关于24MHz无源晶振EMC辐射超标问题,分析与建议如下: 问题描述 某款触屏控制电路板,由于其外置无源贴片晶振SMD3225-4P 24MHz晶振布线不合理,导致EMC辐射超标。 原因分析 EMC三要素是干扰源,被干扰对象和干扰路径。而晶振作为…

24MHz无源晶振EMC辐射超标问题分析与建议

2023-06-15(4引线无源晶振与2引线无源晶振包地图示) 晶诺威科技关于24MHz无源晶振EMC辐射超标问题,分析与建议如下: 问题描述 某款触屏控制电路板,由于其外置无源贴片晶振SMD3225-4P 24MHz晶振布线不合理,导致EMC辐射超标。 原因分析 EMC三要素是干扰源,被干扰对象和干扰路径。而晶振作为… -

; ) 芯片手册要求晶振负载电容是8pF是什么意思?

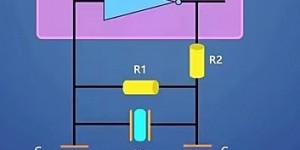

2023-05-26芯片手册要求晶振负载电容是8pF是什么意思? 答:意思是说在晶振选型时,请选择负载电容CL=8pF的石英晶体谐振器,即无源晶振。 解释: 在无源晶振选型时,负载电容CL为无源晶振重要电气参数之一。常见负载电容有6PF、8PF、9PF、12.5PF、9PF、12PF、15PF、18PF、20PF等多种…

芯片手册要求晶振负载电容是8pF是什么意思?

2023-05-26芯片手册要求晶振负载电容是8pF是什么意思? 答:意思是说在晶振选型时,请选择负载电容CL=8pF的石英晶体谐振器,即无源晶振。 解释: 在无源晶振选型时,负载电容CL为无源晶振重要电气参数之一。常见负载电容有6PF、8PF、9PF、12.5PF、9PF、12PF、15PF、18PF、20PF等多种… -

; ) 三防漆导致无源晶振不起振怎么办?

2023-05-20如果三防漆导致无源晶振不起振,晶诺威科技分析原因如下: 原因分析: 1、三防漆可能改变晶振的热传导特性,影响其温度稳定性。需评估温度变化下的性能。 2、确认无源晶振匹配电容是否正确。三防漆可能增加晶振的负载电容,导致频率轻微偏移。设计时应考虑这一因素。 建议改善措施: 1、确认三防漆本身品质是否合格…

三防漆导致无源晶振不起振怎么办?

2023-05-20如果三防漆导致无源晶振不起振,晶诺威科技分析原因如下: 原因分析: 1、三防漆可能改变晶振的热传导特性,影响其温度稳定性。需评估温度变化下的性能。 2、确认无源晶振匹配电容是否正确。三防漆可能增加晶振的负载电容,导致频率轻微偏移。设计时应考虑这一因素。 建议改善措施: 1、确认三防漆本身品质是否合格…