-

; ) 关于芯片外部晶振放置位置的说明

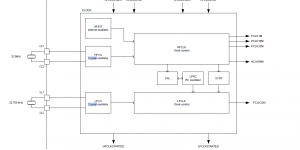

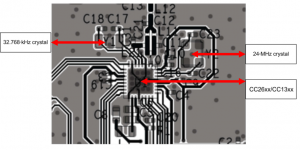

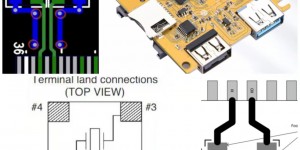

2024-08-22SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os…

关于芯片外部晶振放置位置的说明

2024-08-22SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT 关于芯片外部晶振放置位置,晶诺威科技说明如下: External Oscillator Pins Many microcontrollers have options for at least two os… -

; ) 关于晶振电路抗扰性及优化方案

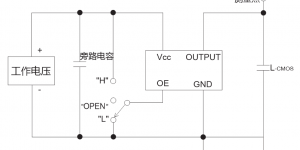

2024-08-17关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…

关于晶振电路抗扰性及优化方案

2024-08-17关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运… -

; ) 电子设计中的EMI和EMC有什么区别?

2024-06-10(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele…

电子设计中的EMI和EMC有什么区别?

2024-06-10(EMI & EMC CIRCUIT DESIGN THROUGH ISOLATION OF AD AND DC) What’s the Difference Between EMI and EMC in Electronic Designs? 电子设计中的EMI和EMC有什么区别? Ele… -

; ) 如何检查晶振安装是否正确?

2024-03-10如何检查晶振安装是否正确? 答:检查晶振是否正确安装,请注意以下三点: 1、确保晶振引脚正确焊接到电路板上,避免虚焊; 2、确保晶振安装在适当且正确的位置,以避免振动和/或冲击; 3、避免电路板上的其他元件与晶振引脚之间的短路或近接。

如何检查晶振安装是否正确?

2024-03-10如何检查晶振安装是否正确? 答:检查晶振是否正确安装,请注意以下三点: 1、确保晶振引脚正确焊接到电路板上,避免虚焊; 2、确保晶振安装在适当且正确的位置,以避免振动和/或冲击; 3、避免电路板上的其他元件与晶振引脚之间的短路或近接。 -

; ) 关于多层PCB设计中晶振接地(GND)问题

2024-01-17关于多层PCB设计中晶振接地(GND)问题,晶诺威科技解释如下: 在多层PCB设计中,合理的层叠设计有助于减小电磁干扰和信号干扰。通常,将信号层与地平面和电源平面隔开,有助于提高信号完整性和降低EMI。 地平面(Ground Plane) 指在电路设计中,用于连接和分布地(Ground)的导电区域。…

关于多层PCB设计中晶振接地(GND)问题

2024-01-17关于多层PCB设计中晶振接地(GND)问题,晶诺威科技解释如下: 在多层PCB设计中,合理的层叠设计有助于减小电磁干扰和信号干扰。通常,将信号层与地平面和电源平面隔开,有助于提高信号完整性和降低EMI。 地平面(Ground Plane) 指在电路设计中,用于连接和分布地(Ground)的导电区域。… -

; ) 关于抗电磁干扰(EMI)晶振的选择

2023-12-25抗电磁干扰(EMI)晶振 晶诺威科技针对电磁干扰(EMI)问题,研发了具有抗干扰特性的晶振。该类晶振通过采用特殊的电路设计、材料选择及制造工艺,有效提高了自身的抗电磁干扰能力。其输出频率具备高精度和高稳定度,因此可以为IC提供精准和稳定的参考时钟。 针对RF射频类电子产品,如蓝牙、WiFi等短距离无…

关于抗电磁干扰(EMI)晶振的选择

2023-12-25抗电磁干扰(EMI)晶振 晶诺威科技针对电磁干扰(EMI)问题,研发了具有抗干扰特性的晶振。该类晶振通过采用特殊的电路设计、材料选择及制造工艺,有效提高了自身的抗电磁干扰能力。其输出频率具备高精度和高稳定度,因此可以为IC提供精准和稳定的参考时钟。 针对RF射频类电子产品,如蓝牙、WiFi等短距离无… -

; ) STM 32.768KHz低速外部时钟典型应用说明

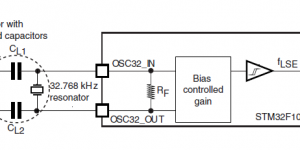

2023-12-16(Typical application with a 32.768 kHz crystal) STM 32.768KHz 低速外部时钟典型应用说明 The low-speed external (LSE) clock can be supplied with a 32.768 KHz crysta…

STM 32.768KHz低速外部时钟典型应用说明

2023-12-16(Typical application with a 32.768 kHz crystal) STM 32.768KHz 低速外部时钟典型应用说明 The low-speed external (LSE) clock can be supplied with a 32.768 KHz crysta… -

; ) 数字电路中信号异常及可能原因

2023-12-13关于数字电路中信号异常及可能原因,晶诺威科技归纳如下: 1、幅值异常 波形不稳定,导致无法判定高低电平。 可能原因: 负载太大 走线过长 驱动太小 电平异常 2、过冲/回冲 方波过冲/回冲过高。超出正常电平10%。 可能原因: 驱动过高 存在反射 自激振荡 检查去耦 避免晶体振荡器输出波形失真的对策…

数字电路中信号异常及可能原因

2023-12-13关于数字电路中信号异常及可能原因,晶诺威科技归纳如下: 1、幅值异常 波形不稳定,导致无法判定高低电平。 可能原因: 负载太大 走线过长 驱动太小 电平异常 2、过冲/回冲 方波过冲/回冲过高。超出正常电平10%。 可能原因: 驱动过高 存在反射 自激振荡 检查去耦 避免晶体振荡器输出波形失真的对策… -

; ) 晶振在PCBA上的位置很重要吗?

2023-10-09晶振在PCBA上的位置很重要吗? 答:是的。在电路板上晶振的位置很重要。 晶诺威科技解释如下: 由于晶振内部存在石英晶体,受到外部撞击或强烈振荡等情况造成晶体断裂,很容易造成晶振不起振,所以通常在电路设计时,要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等地方。 关于建议晶振接地的原因 在电…

晶振在PCBA上的位置很重要吗?

2023-10-09晶振在PCBA上的位置很重要吗? 答:是的。在电路板上晶振的位置很重要。 晶诺威科技解释如下: 由于晶振内部存在石英晶体,受到外部撞击或强烈振荡等情况造成晶体断裂,很容易造成晶振不起振,所以通常在电路设计时,要考虑晶振的可靠安装,其位置尽量不要靠近板边、设备外壳等地方。 关于建议晶振接地的原因 在电… -

; ) 如何消除有源晶振副波干扰?

2023-10-07如何消除有源晶振副波干扰?晶诺威科技解释如下: 1、 晶振外壳接地(通过接地引脚)设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。 2、 晶振所在层铺地设计,目的是防止晶振信号干扰其它层。 3、 不要在电路板边缘设计安置晶振,以防止短路。 4、 若晶振位于电路板较边缘的位置,晶振与参考接地…

如何消除有源晶振副波干扰?

2023-10-07如何消除有源晶振副波干扰?晶诺威科技解释如下: 1、 晶振外壳接地(通过接地引脚)设计,目的是防止晶振信号的向外辐射,同时屏蔽外来杂波干扰。 2、 晶振所在层铺地设计,目的是防止晶振信号干扰其它层。 3、 不要在电路板边缘设计安置晶振,以防止短路。 4、 若晶振位于电路板较边缘的位置,晶振与参考接地…