-

; ) 晶振不起振的原因分析

2022-02-22单片机晶振的作用是为系统提供基本的时钟信号。通常一个系统共用一个晶振,便于各部分保持同步。不同型号的单片机使用的石英晶振型号及频率也可能是不一样的。单片机中的晶振若是出了问题,单片机也就无法正常工作了。以下我们从晶振及电路应用两个方面来分析可能造成晶振不起振的原因。 关于晶振方面: 1、晶振的选型,…

晶振不起振的原因分析

2022-02-22单片机晶振的作用是为系统提供基本的时钟信号。通常一个系统共用一个晶振,便于各部分保持同步。不同型号的单片机使用的石英晶振型号及频率也可能是不一样的。单片机中的晶振若是出了问题,单片机也就无法正常工作了。以下我们从晶振及电路应用两个方面来分析可能造成晶振不起振的原因。 关于晶振方面: 1、晶振的选型,… -

; ) 为何晶振布置在PCB边缘时会导致辐射超标?

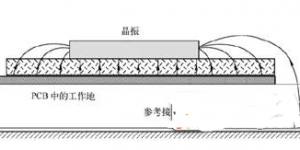

2022-02-22为何晶振布置在PCB边缘时会导致辐射超标? 如上图所示:当晶振布置在PCB中间或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在PCB内部,分布到参考接地板的电场大大减小,从而导致晶振与参考接地板之间的寄生电容大大减小。反之,若晶振布置…

为何晶振布置在PCB边缘时会导致辐射超标?

2022-02-22为何晶振布置在PCB边缘时会导致辐射超标? 如上图所示:当晶振布置在PCB中间或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在PCB内部,分布到参考接地板的电场大大减小,从而导致晶振与参考接地板之间的寄生电容大大减小。反之,若晶振布置… -

; ) 数字电路的时钟信号源:无源晶振电路与有源晶振电路对比

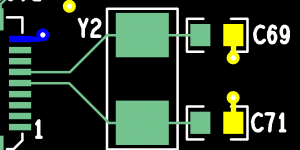

2022-01-10关于数字电路的时钟信号源:无源晶振电路与有源晶振电路对比如下: 对于数字电路中基于时钟信号才能工作的芯片来说,有两种选择: 芯片内置时钟电路,通过编程器配置或外部设置就能产生时钟信号,内部时钟往往频率精度较低。 外接晶振电路产生时钟信号。由晶振提供的时钟信号具备高精度及高稳定性等特点。 外部晶振…

数字电路的时钟信号源:无源晶振电路与有源晶振电路对比

2022-01-10关于数字电路的时钟信号源:无源晶振电路与有源晶振电路对比如下: 对于数字电路中基于时钟信号才能工作的芯片来说,有两种选择: 芯片内置时钟电路,通过编程器配置或外部设置就能产生时钟信号,内部时钟往往频率精度较低。 外接晶振电路产生时钟信号。由晶振提供的时钟信号具备高精度及高稳定性等特点。 外部晶振… -

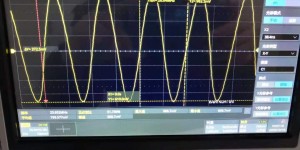

; ) 晶体谐振器驱动电平/激励功率(Drive level)概念,计算及测量方法

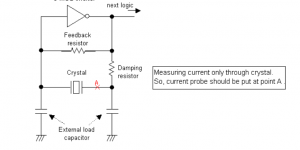

2021-12-24(电流探头测试点应该在电路的A位置) 驱动电平/激励功率(Drive level)概念 驱动电平指振荡电路工作时晶体谐振器的功耗。晶体必须保持在驱动电平规格范围内,过高的驱动电平可能会导致频率和等效串联电阻的意外变化。 驱动电平/激励功率(Drive level)计算方法 驱动电平 = I^2・R1…

晶体谐振器驱动电平/激励功率(Drive level)概念,计算及测量方法

2021-12-24(电流探头测试点应该在电路的A位置) 驱动电平/激励功率(Drive level)概念 驱动电平指振荡电路工作时晶体谐振器的功耗。晶体必须保持在驱动电平规格范围内,过高的驱动电平可能会导致频率和等效串联电阻的意外变化。 驱动电平/激励功率(Drive level)计算方法 驱动电平 = I^2・R1… -

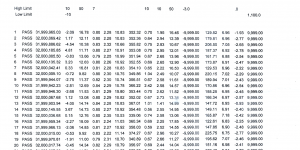

; ) 如何计算10PPM 12PF 32M晶振的频偏范围?

2021-12-21首先需要指出的是: ±10PPM 12PF 32M晶振频偏不是直接算出来的,而是先使用晶振测试仪器测量出实际输出频率,才可以计算得出晶振频偏多少。 这里涉及到晶振的几个常用术语:晶振精度、调整频差、温度频差、频率偏差(频差)及频偏超差。 晶振精度其实指的是晶振的两个电气参数:调整频差和温度频差。 调…

如何计算10PPM 12PF 32M晶振的频偏范围?

2021-12-21首先需要指出的是: ±10PPM 12PF 32M晶振频偏不是直接算出来的,而是先使用晶振测试仪器测量出实际输出频率,才可以计算得出晶振频偏多少。 这里涉及到晶振的几个常用术语:晶振精度、调整频差、温度频差、频率偏差(频差)及频偏超差。 晶振精度其实指的是晶振的两个电气参数:调整频差和温度频差。 调… -

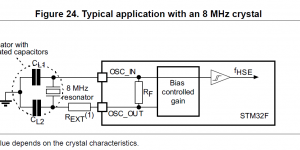

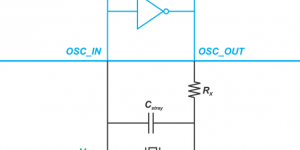

; ) 晶振电路的外部电阻R Ext计算公式

2021-11-15晶振电路外部电阻R Ext的作用是限制晶振电路的驱动大小,防止晶体被过分驱动造成晶体老化或损坏。并且它与CL2构成一个低通滤波器,以确保振荡器的起振频点在基频而不是其它倍频频点。如果芯片商给出的晶振电路的驱动功率小于1mw,那么R Ext就不需要使用了,它的值可以是0欧姆;如果芯片商给出的晶振电路的…

晶振电路的外部电阻R Ext计算公式

2021-11-15晶振电路外部电阻R Ext的作用是限制晶振电路的驱动大小,防止晶体被过分驱动造成晶体老化或损坏。并且它与CL2构成一个低通滤波器,以确保振荡器的起振频点在基频而不是其它倍频频点。如果芯片商给出的晶振电路的驱动功率小于1mw,那么R Ext就不需要使用了,它的值可以是0欧姆;如果芯片商给出的晶振电路的… -

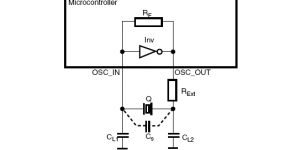

; ) 晶振电路的反馈电阻RF

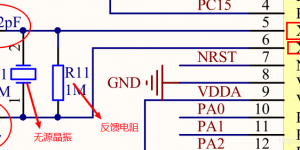

2021-11-05(无源晶振电路) 在无源晶振电路中,反相器的增益必须在一定的范围内才能使晶体起振,不能过大也不能过小,针对MHz电路反馈电阻一般取值1MΩ;针对KHz电路反馈电阻一般取值10MΩ。在设计中经常在反相器两端串接一个比较大的反馈电阻RF(Feedback Resistance),用以调节反相器的增益,使…

晶振电路的反馈电阻RF

2021-11-05(无源晶振电路) 在无源晶振电路中,反相器的增益必须在一定的范围内才能使晶体起振,不能过大也不能过小,针对MHz电路反馈电阻一般取值1MΩ;针对KHz电路反馈电阻一般取值10MΩ。在设计中经常在反相器两端串接一个比较大的反馈电阻RF(Feedback Resistance),用以调节反相器的增益,使… -

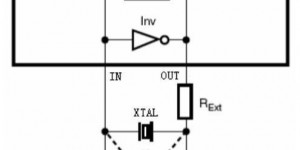

; ) 晶振电容三点式振荡电路:晶振 Pierce电路

2021-11-03大多数晶振电路都是采用电容三点式振荡电路,Pierce电路就是其中一种应用最广泛的电路,它的电路结构如下图: (晶振电路的 Pierce电路) 其中, Inv:芯片内部反相器; RF:反馈电阻,一般集成在芯片内部,也有的芯片内部不集成RF; XTAL:石英晶体; CL1、CL2:补偿负载电容; CS…

晶振电容三点式振荡电路:晶振 Pierce电路

2021-11-03大多数晶振电路都是采用电容三点式振荡电路,Pierce电路就是其中一种应用最广泛的电路,它的电路结构如下图: (晶振电路的 Pierce电路) 其中, Inv:芯片内部反相器; RF:反馈电阻,一般集成在芯片内部,也有的芯片内部不集成RF; XTAL:石英晶体; CL1、CL2:补偿负载电容; CS… -

; ) 无源晶振起振条件:振幅起振条件与相位起振条件

2021-10-29在晶振电路中,当环路增益大于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号相比于原来的信号在幅度上要大。这时振荡回路中的信号经过反复反馈放大后,不断增大,最终驱动晶体振荡。 起振条件也有两层意思: 1、振幅起振条件: 振幅跟振动回路有关,主要由IC电压决定。 表示输出信号振幅大于输入…

无源晶振起振条件:振幅起振条件与相位起振条件

2021-10-29在晶振电路中,当环路增益大于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号相比于原来的信号在幅度上要大。这时振荡回路中的信号经过反复反馈放大后,不断增大,最终驱动晶体振荡。 起振条件也有两层意思: 1、振幅起振条件: 振幅跟振动回路有关,主要由IC电压决定。 表示输出信号振幅大于输入… -

; ) 晶振电路的平衡条件:振幅平衡与相位平衡

2021-10-25在晶振电路中,当环路增益等于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号和原来的信号一模一样,这时振荡器才有持续的稳定的振荡信号输出,振荡回路达到平衡状态。从另一个角度来分析,可以认为,即使没有输入信号,回路也有输出。 平衡条件有两层意思: 1、振幅平衡条件 表示输入输出的幅度一致…

晶振电路的平衡条件:振幅平衡与相位平衡

2021-10-25在晶振电路中,当环路增益等于1时,说明输出信号经反馈回路和放大回路放大后,回到输出端的信号和原来的信号一模一样,这时振荡器才有持续的稳定的振荡信号输出,振荡回路达到平衡状态。从另一个角度来分析,可以认为,即使没有输入信号,回路也有输出。 平衡条件有两层意思: 1、振幅平衡条件 表示输入输出的幅度一致…