-

; ) 关于晶振电路抗扰性及优化方案

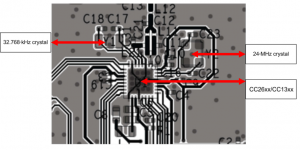

2024-08-17关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运…

关于晶振电路抗扰性及优化方案

2024-08-17关于晶振电路抗扰性及优化方案,晶诺威科技解释如下: 电路抗扰性不良也是晶振失效的常见原因之一。电路抗扰性差意味着电子设备容易受到干扰,这会直接影响晶振的工作。 1、电源噪声 电源噪声是电路抗扰性不良的一个重要因素。电源声会引起晶振的频率变化,导致晶振失效。此外,电源噪声还会引发电路中其他元件的异常运… -

; ) 为何晶振布置在PCB边缘时会导致辐射超标?

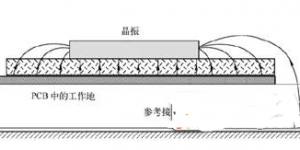

2022-02-22为何晶振布置在PCB边缘时会导致辐射超标? 如上图所示:当晶振布置在PCB中间或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在PCB内部,分布到参考接地板的电场大大减小,从而导致晶振与参考接地板之间的寄生电容大大减小。反之,若晶振布置…

为何晶振布置在PCB边缘时会导致辐射超标?

2022-02-22为何晶振布置在PCB边缘时会导致辐射超标? 如上图所示:当晶振布置在PCB中间或离PCB边缘较远时,由于PCB中工作地(GND)平面的存在,使大部分的电场控制在晶振与工作地(GND)之间,即在PCB内部,分布到参考接地板的电场大大减小,从而导致晶振与参考接地板之间的寄生电容大大减小。反之,若晶振布置… -

; ) 如何减少寄生电容对晶振造成的辐射干扰?

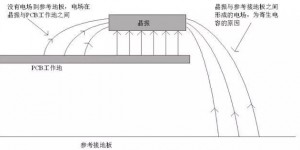

2021-06-15若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越…

如何减少寄生电容对晶振造成的辐射干扰?

2021-06-15若晶振正好布线于电路板边缘,当产品放置于辐射发射的测试环境中时,被测产品的高速器件与参考地会形成一定的容性耦合,产生寄生电容,导致出现共模辐射,寄生电容越大,共模辐射越强;而寄生电容实质就是晶振与参考地之间的电场分布,当两者之间电压恒定时,两者之间电场分布越多,两者之间电场强度就越大,寄生电容也会越…