-

; ) 不同晶振及晶振电路产生的相位噪声phase noise原因及分析

2021-08-09关于不同晶振及晶振电路产生的相位噪声phase noise原因,晶诺威科技分析如下: 在低噪声晶振设计中,电路是非常重要的环节,振荡电路应该要使晶振的有载Q值不致下降很多,并且电路附加的噪声要足够小。 有源晶振常见的类型为普通晶振XO,温补晶振TCXO,恒温晶振OCXO,他们之间直观的不同,就是频率…

不同晶振及晶振电路产生的相位噪声phase noise原因及分析

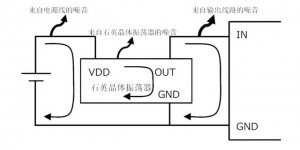

2021-08-09关于不同晶振及晶振电路产生的相位噪声phase noise原因,晶诺威科技分析如下: 在低噪声晶振设计中,电路是非常重要的环节,振荡电路应该要使晶振的有载Q值不致下降很多,并且电路附加的噪声要足够小。 有源晶振常见的类型为普通晶振XO,温补晶振TCXO,恒温晶振OCXO,他们之间直观的不同,就是频率… -

; ) 减少晶振周边电路相噪phase noise的两项最重要方法

2021-08-06晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。 减少晶振周边电路相噪的方法主要有以下两点: 缩短输岀线路 输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度…

减少晶振周边电路相噪phase noise的两项最重要方法

2021-08-06晶振周围电路的合适设计对减少相噪noise极为重要。只要电路设计妥善适宜,即可很大程度避免相噪问题,从而充分发挥电子元器件本身所具有的性能。 减少晶振周边电路相噪的方法主要有以下两点: 缩短输岀线路 输出线路是电路中最容易释放相噪的部分。为此,在设计电路图案之际,应当最优先设计输岀线路部分,采用长度… -

; ) 如何通过串联电阻降低晶振相噪phase noise,避免输出波形output waveform失真?

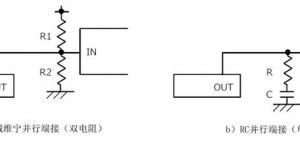

2021-08-05串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍 主要分为连接串联电阻与连接终端电阻两部分: 连接串联电阻: 晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必…

如何通过串联电阻降低晶振相噪phase noise,避免输出波形output waveform失真?

2021-08-05串联电阻降低晶振相噪(phase noise)避免输出波形(output waveform)失真方法介绍 主要分为连接串联电阻与连接终端电阻两部分: 连接串联电阻: 晶振连接输入对象的元器件时,通常产生过冲、下冲或振铃等波形变形。这些变形的波形中含有振荡频率的约3-7倍的射频成份,将引发相噪,所以必… -

; ) 在晶振应用中,什么是抖动Jitter和相位噪声phase noise?

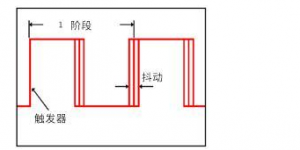

2021-08-04在晶振应用中,什么是抖动和相位噪声? 抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的 bit 周期都非常短,一般在几百 ps 甚至几十 ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。 实际信号可能具有较高复杂性,比如既有随机抖动…

在晶振应用中,什么是抖动Jitter和相位噪声phase noise?

2021-08-04在晶振应用中,什么是抖动和相位噪声? 抖动(Jitter)反映的是数字信号偏离其理想位置的时间偏差。高频数字信号的 bit 周期都非常短,一般在几百 ps 甚至几十 ps,很小的抖动都会造成信号采样位置电平的变化,所以高频数字信号对于抖动都有严格的要求。 实际信号可能具有较高复杂性,比如既有随机抖动… -

; ) 晶振的相位噪声指的是什么?

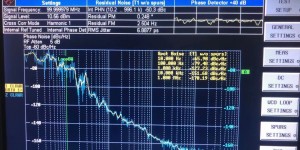

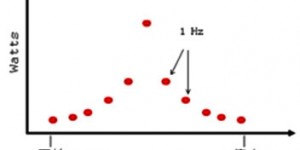

2020-08-18关于相位噪声Phase noise的定义 在频域上,数据偏移量用相位噪声来定义。对于频率为f0的时钟信号而言,如果信号上不含抖动,则信号的所有功率应集中在频率点f0处,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。信号…

晶振的相位噪声指的是什么?

2020-08-18关于相位噪声Phase noise的定义 在频域上,数据偏移量用相位噪声来定义。对于频率为f0的时钟信号而言,如果信号上不含抖动,则信号的所有功率应集中在频率点f0处,由于任何信号都存在抖动,这些抖动有些是随机的,有些是确定的,分布于相当广的频带上,因此抖动的出现将使信号功率被扩展到这些频带上。信号…